数电笔记

0基本半导体器件

0.1半导体二极管

0.1.1二极管特性

注:书上是将PN结和半导体二极管分开讲,因为两者很多特性相似,故在这里和在一起。

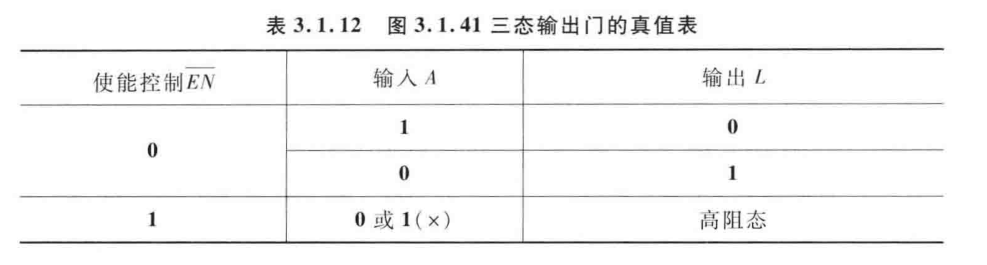

1.伏安特性

PN结的理想伏安特性:

- V : PN结外加电压

- k : 玻尔兹曼常数

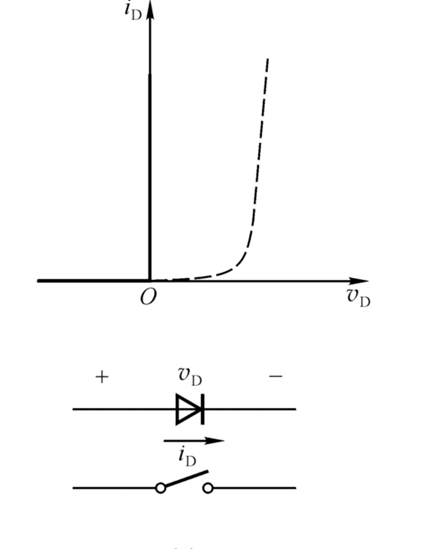

(a)硅二极管的伏安特性曲线,虚线为PN结的理想伏安特性

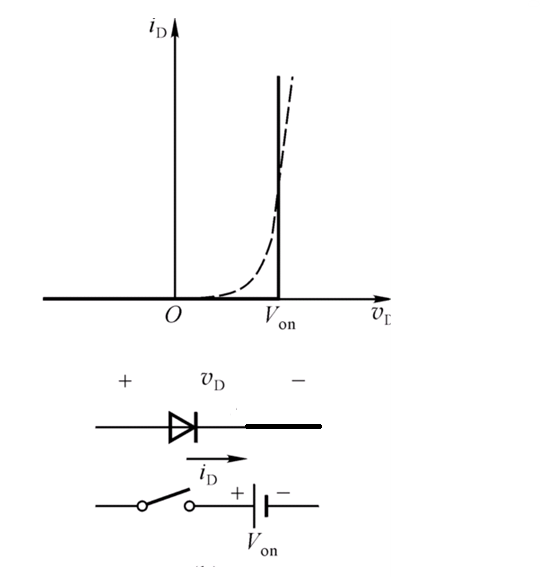

(b)锗二极管的伏安特性曲线

(a)硅二极管的伏安特性曲线,虚线为PN结的理想伏安特性

(b)锗二极管的伏安特性曲线

2.正向、3.反向特性

| 硅管 | 锗管 | ||

|---|---|---|---|

| 2.正向特性 | 开启电压(门坎电压)Vth | 0.5V | 0.1V |

| 导通压降 | 0.6V-0.8V(0.7V) | 0.2-0.3V(0.3V) | |

| 3.反向特性 | 反向电流 | nA数量级 | uA数量级 |

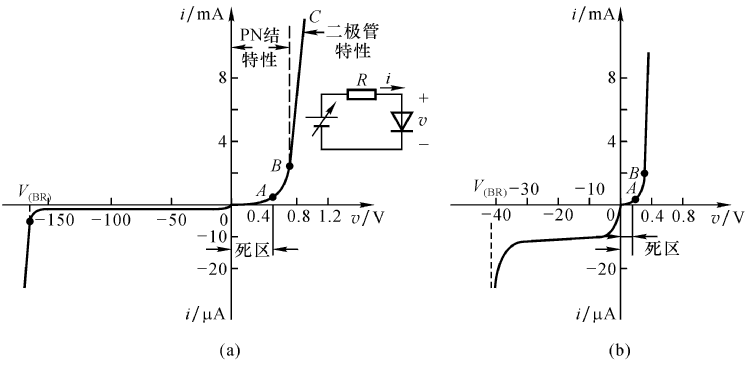

4.温度特性

PN结温度升高时:

反向饱和电流

温度每升高

正向电流升高(相当与保持正向电流不变,所需的正偏压减少)--PN结正向电压具有负温度特性

为保证PN结正常工作,有最高结温的限制: 硅半导体:

5.反向击穿特性

- 雪崩击穿--发生在低掺杂的PN结中,反向击穿电压较高(大于7V) 温度系数为正

- 齐纳击穿--发生在高掺杂的PN结中,反向击穿电压较低(小于4V)

- 在4~7V时,上述两种击穿可同时存在 反向击穿后应限制反向电流的增加

6.电容效应

PN结电容

正向偏置时,以

7. 其他参数

- 正向最大整流电流

- 反向击穿电压

- 反向电流

- 结电容

0.1.2二极管模型

非线性器件,进行线性化处理

(1) 理想模型

(2)大信号模型

(3)小信号模型

当

二极管基本应用电路分析例子

- 全波整流电路、桥式整流电路

- 限幅保护电路

- 门电路

- 低压稳压电路

0.1.3特种二极管

TODO 此处未整理完,以后再加

稳压二极管等,以后再理

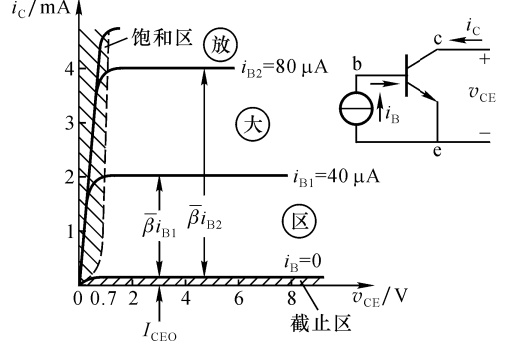

0.2半导体三极管

BJT:双极性晶体管(英语:bipolar transistor),全称双极性结型晶体管(bipolar junction transistor, BJT),简称晶体管,俗称三极管。

结构与类型:NPN与PNP两种 从材料组成: 硅三极管(NPN),锗三极管(PNP)

工作时PN结的条件

发射结正向偏置,集电结反向偏置—放大状态

发射结正向偏置,集电结正向偏置—饱和状态

发射结反向偏置,集电结正向偏置—倒置工作状态

发射结反向偏置,集电结反向偏置—截止状态

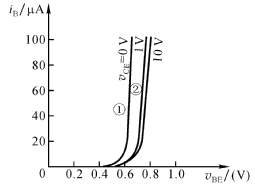

曲线

输入特性曲线

工作状态的判断

方法1:

当三极管导通时,先假设放大状态进行计算,若计算结果

0.3场效应管

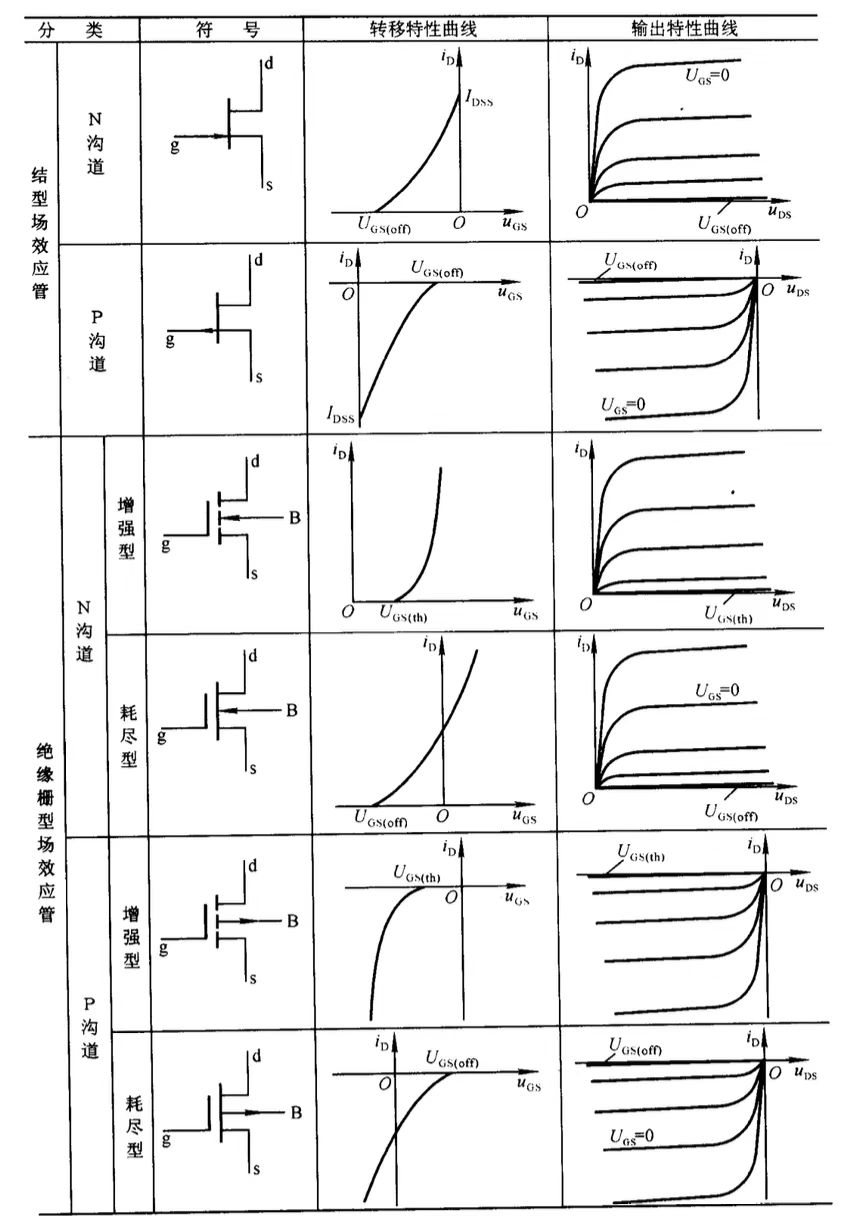

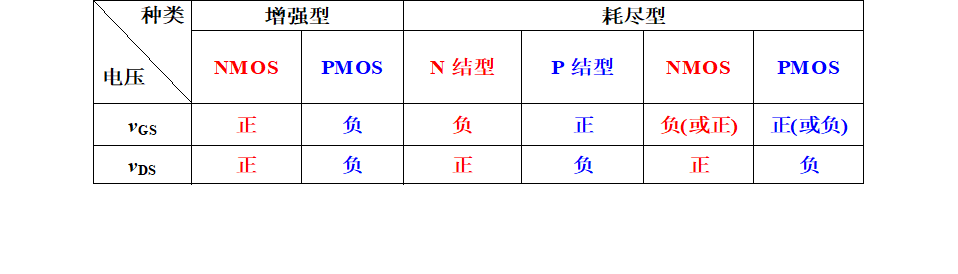

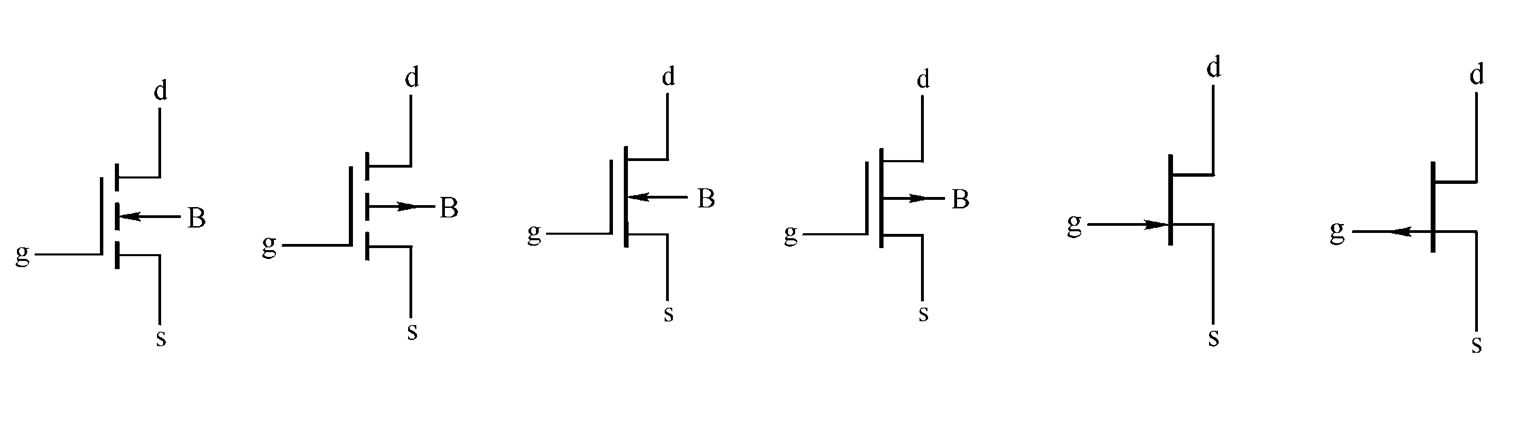

0.3.1各种场效应管

0.3.2伏安特性与电流方程

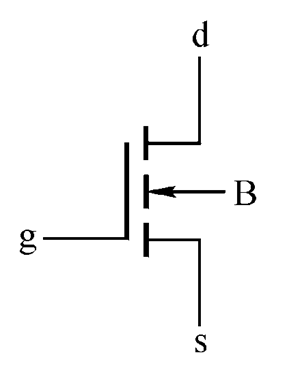

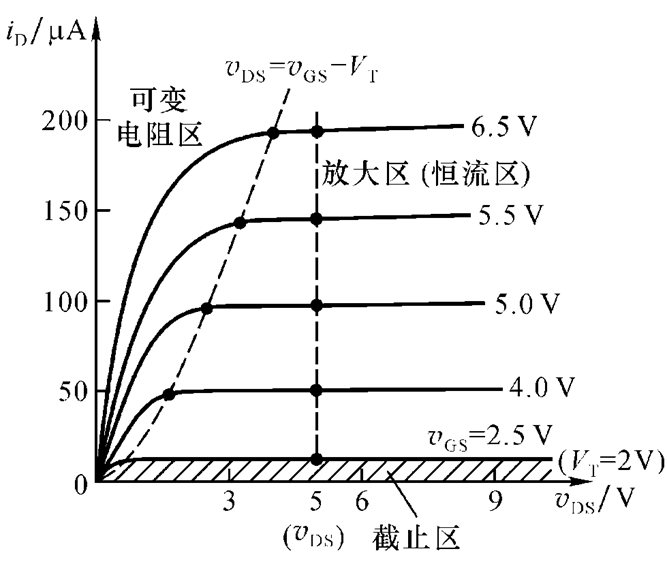

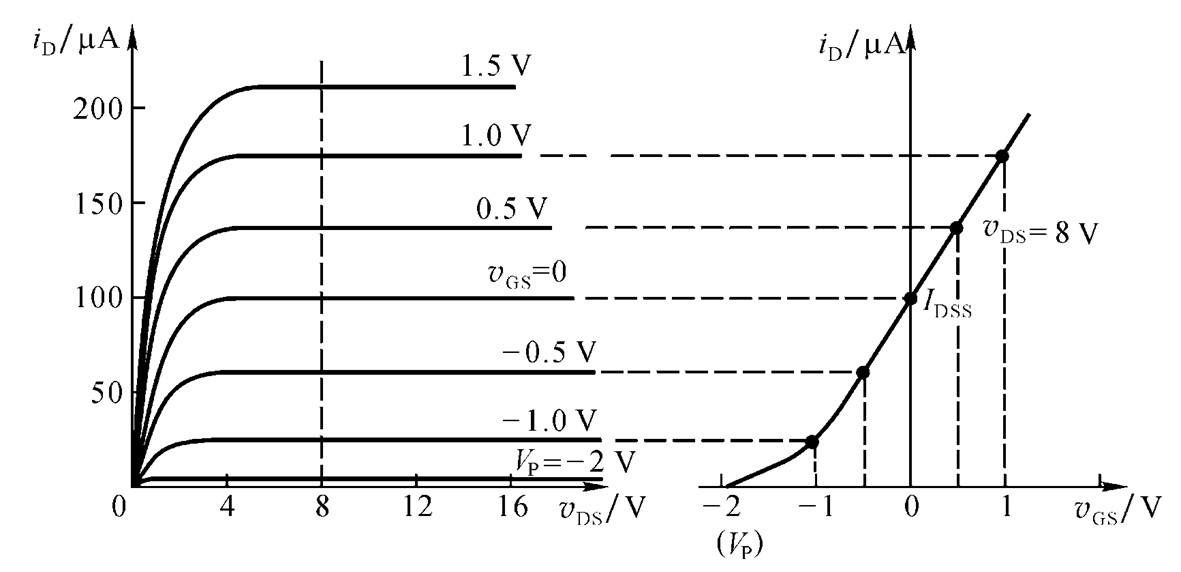

(1) 输出特性(漏极特性)

表示漏极电流iD与漏-源电压vDS之间的关系

特性与三极管相似,分为 3个工作区,但工作区的作用有所不同。 - 可变电阻区 - 放大区(恒流区、饱和区) - 截止区(夹断区)

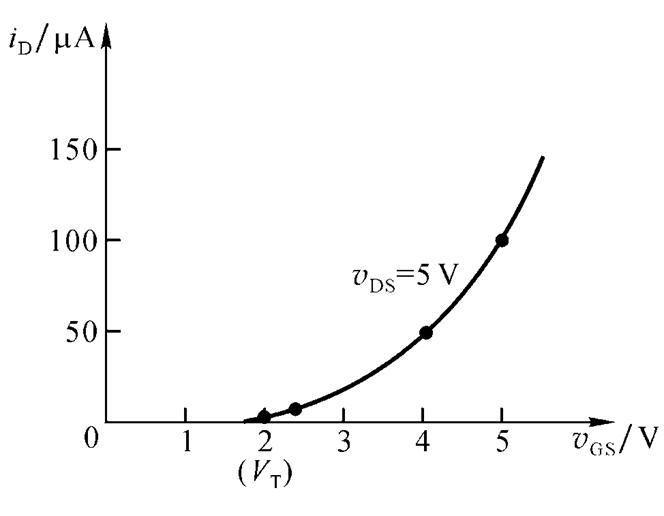

(2) 增强型NMOS管的转移特性

(增强型PMOS管的控制特性与NMOS管相同,除了电压电流极性相反)

在一定

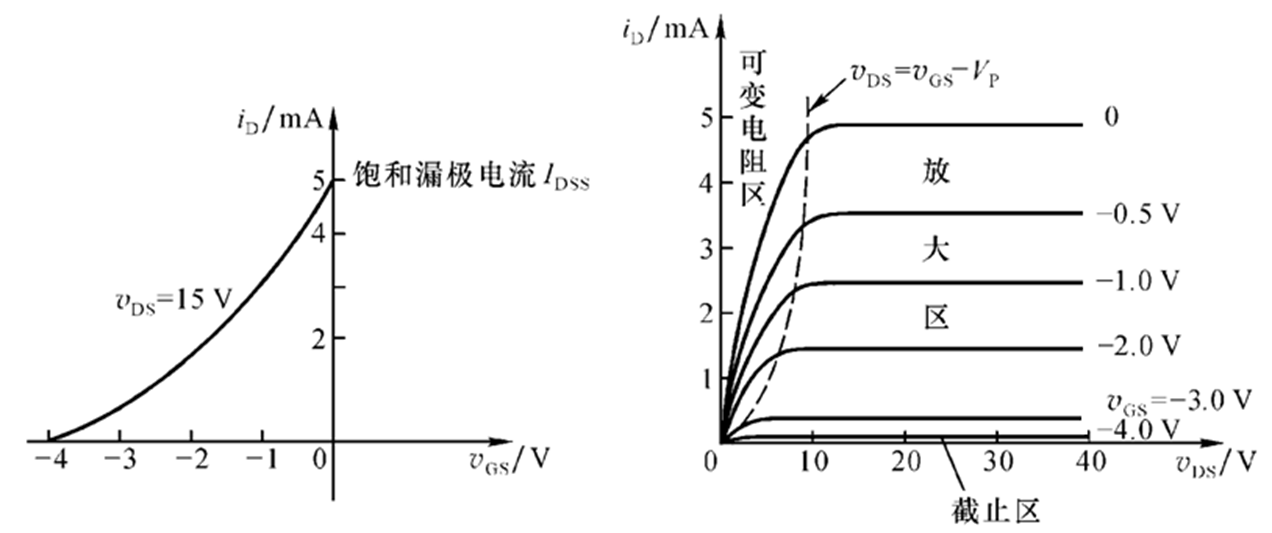

(3) 耗尽型NMOS的伏安特性

(4)JFET的伏安特性(以N沟道JFET为例)

伏安特性曲线和电流方程与耗尽型MOSFET相似。但要求

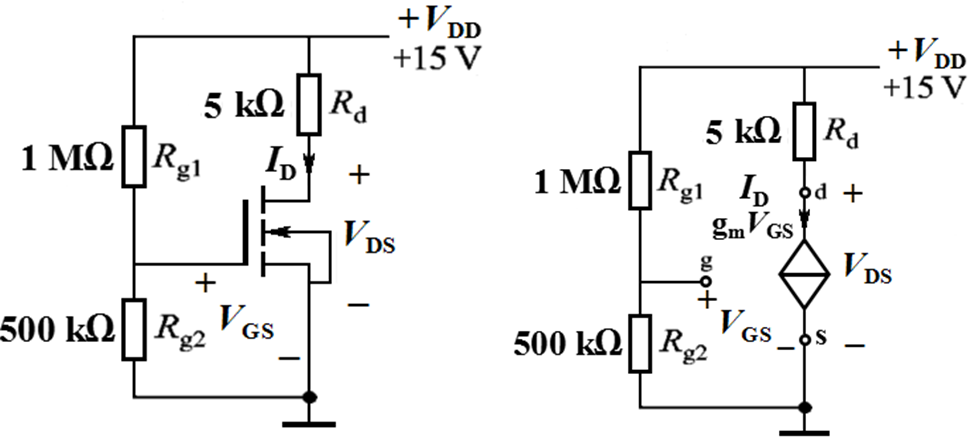

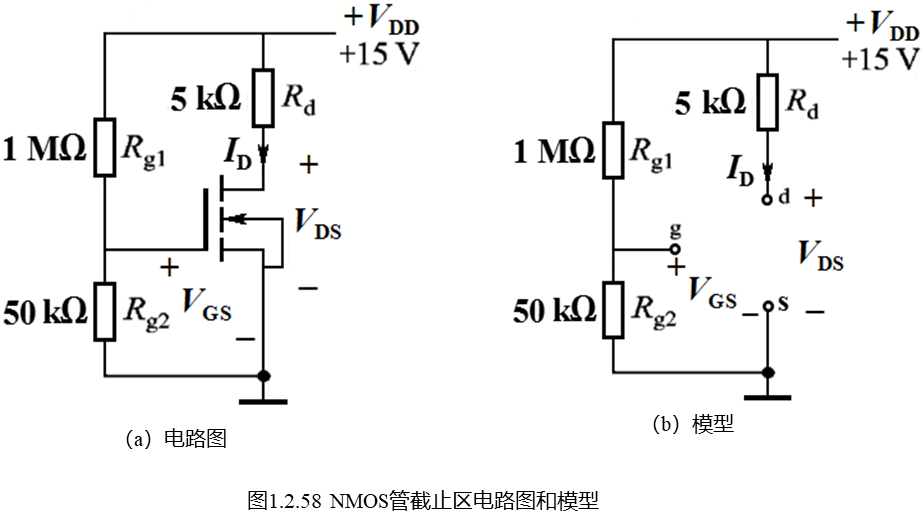

0.3.3场效应管的工作状态

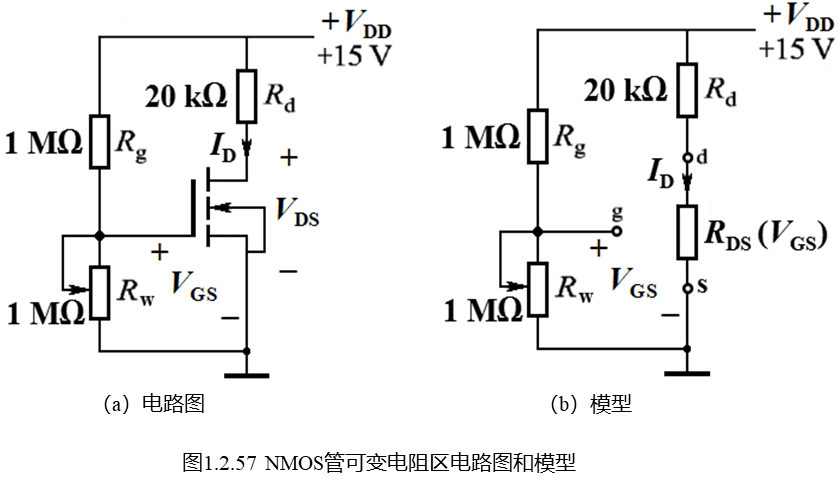

(1) 可变电阻区

管子导通,但尚未预夹断

不同FET类型对偏置电压的要求:

(2) 放大区(恒流区、饱和区)

(3) 夹断区(截止区)

3.1数字逻辑基础

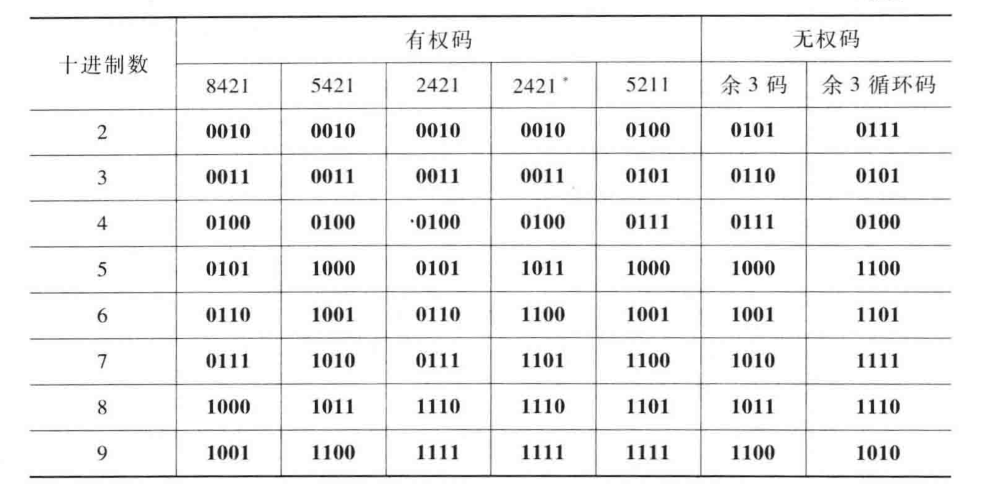

3.1.1数字电路中的编码

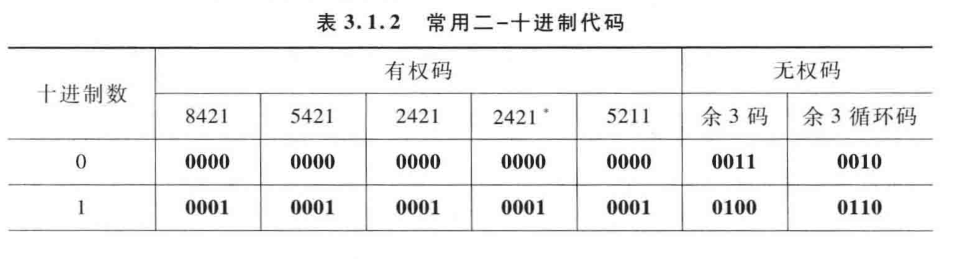

二-十进制编码(BCD码)

BCD码是将十进制数中的10个数字分别用一组4位二进制数代替,俗称二-十进制代码(BCD Binary coded number) 常用的二-十进制代码如下表所示:

| 十进制数 | 8421码 | 5421码 | 2421码 | 余3码 | 余3循环码 | |

|---|---|---|---|---|---|---|

| 0 | 0000 | 0000 | 0000 | 0011 | 0010 | |

| 1 | 0001 | 0001 | 0001 | 0100 | 0110 | |

| 2 | 0010 | 0010 | 0010 | 0101 | 0111 | |

| 3 | 0011 | 0011 | 0011 | 0110 | 0101 | |

| 4 | 0100 | 0100 | 0100 | 0111 | 0100 | |

| 5 | 0101 | 1000 | 1011 | 1000 | 1100 | |

| 6 | 0110 | 1001 | 1100 | 1001 | 1101 | |

| 7 | 0111 | 1010 | 1101 | 1010 | 1111 | |

| 8 | 1000 | 1011 | 1110 | 1011 | 1110 | |

| 9 | 1001 | 1100 | 1111 | 1100 | 1010 |

符号数的编码表示

- 原码

- 反码

一个4位二进制数,它的最大数是10000,那么在这个最大数以内的任何一个数,如0101,它的最大数之间有以下关系,即

此时,最大数10000称为模,而1011和(-0101)对最大数而言,互为补码(对1011的每一位求反后加1,即课构成它的补码)

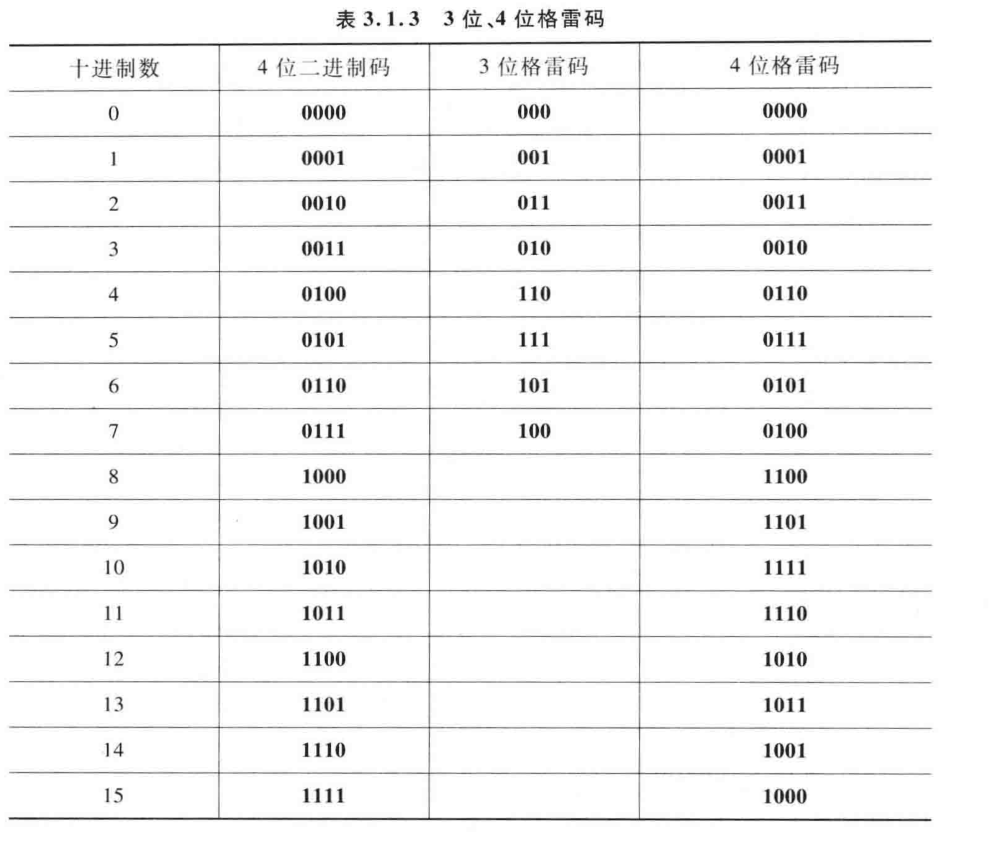

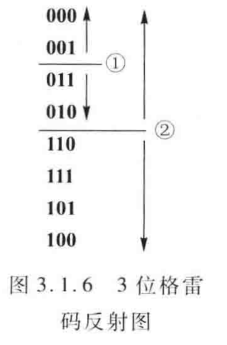

- 格雷码(Gray code) 任何相邻的两组代码之间只有一位码元不同,其他码元完全相同。

| 格雷码具有循环的效果,所以又有循环码和可靠性编码的叫法。 根据格雷码的编码规则,格雷码可以通过反射映射得到,3 位格雷码的反射过程如图 3.1.6 所示。 二进制数码 0、1 经第一次反射,得到 2 位格雷码。再经第二次反射,得到 3 位格雷码,依次类推。 |

|

3.1.2数字电路中的基本功能电路

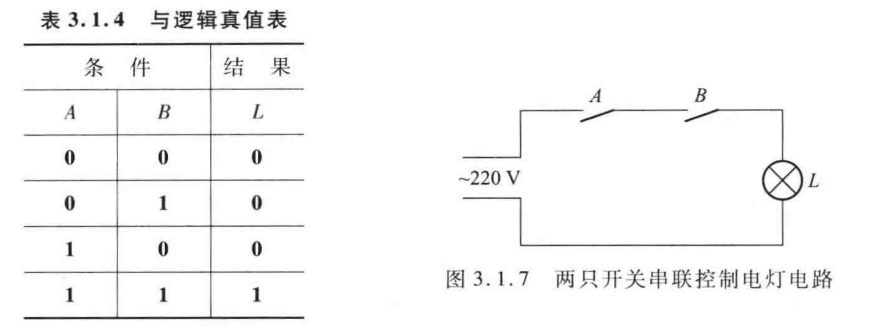

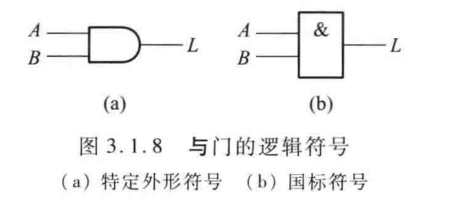

1.与逻辑关系

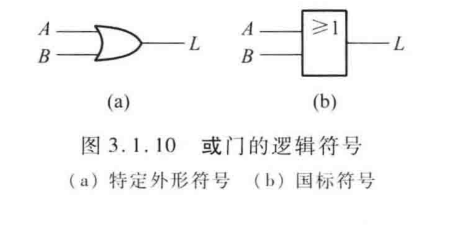

2.与逻辑关系

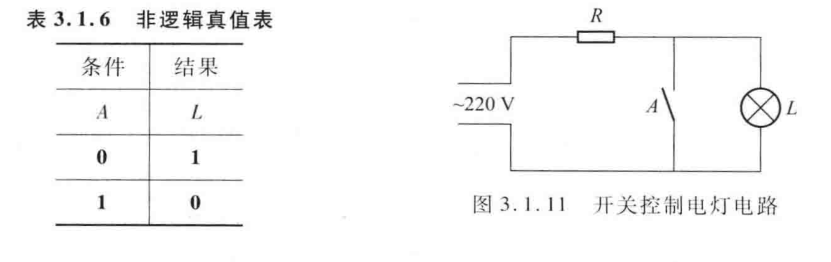

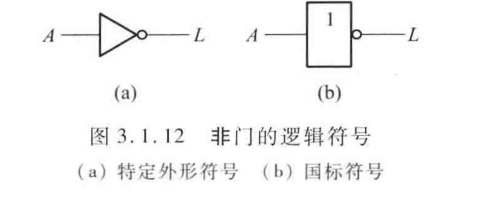

3.非逻辑关系

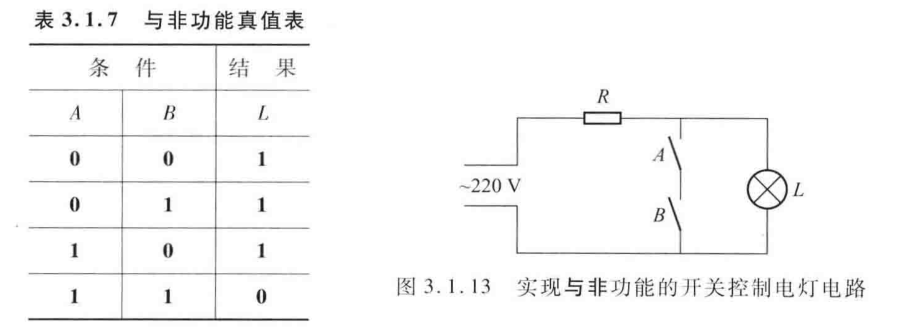

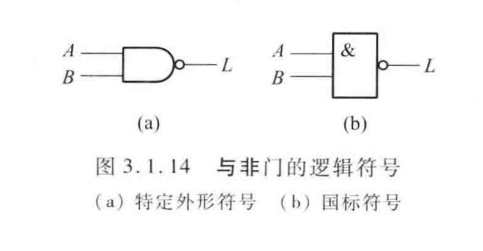

4.与非逻辑关系

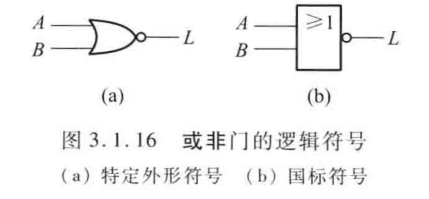

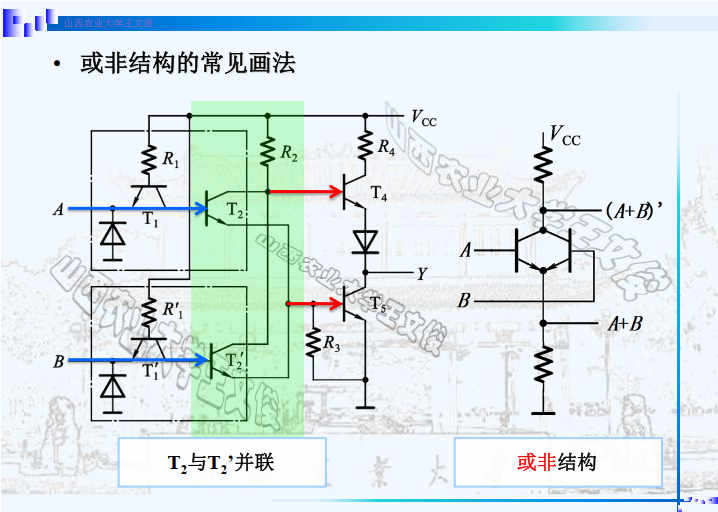

5.或非逻辑关系

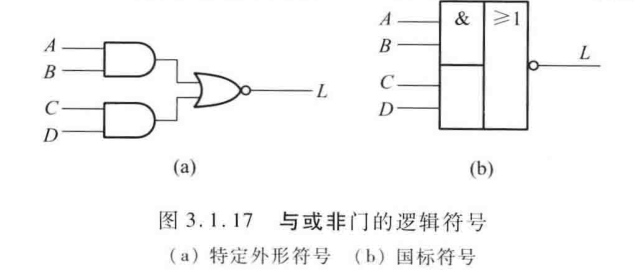

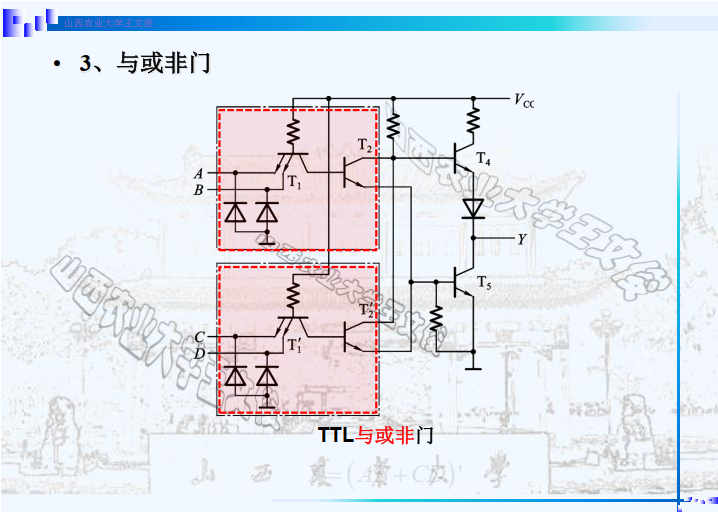

6.与或非逻辑功能

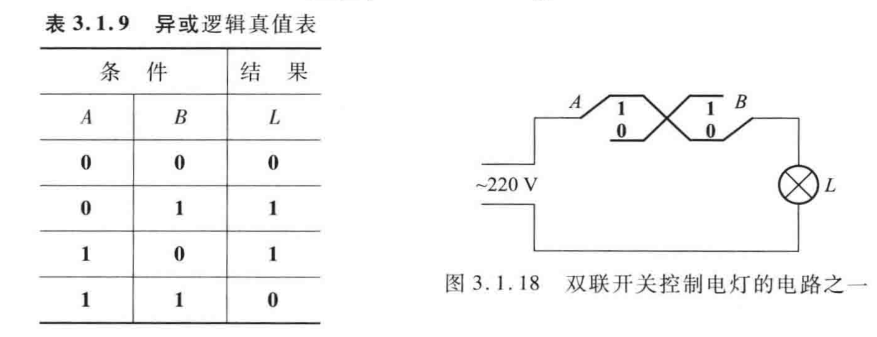

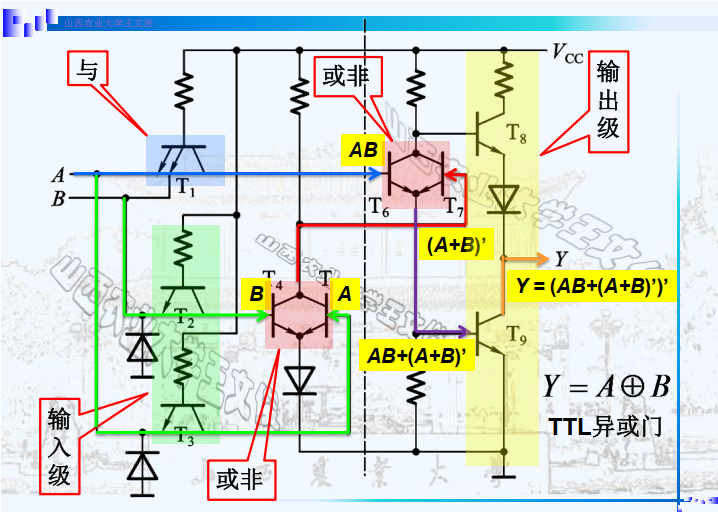

7.异或逻辑功能

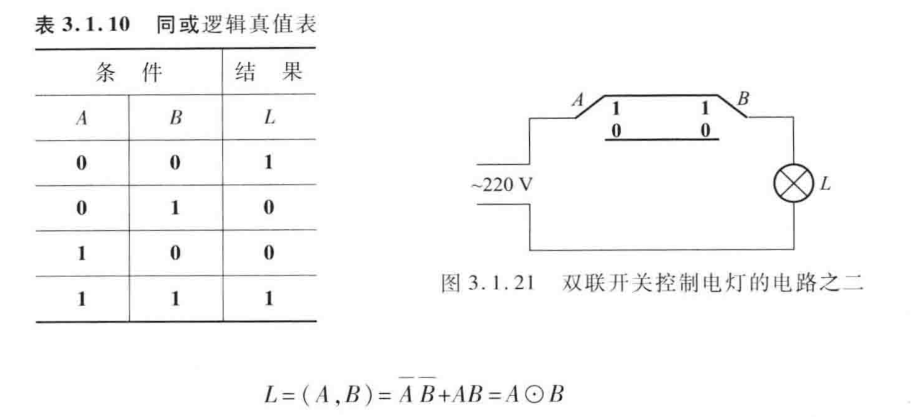

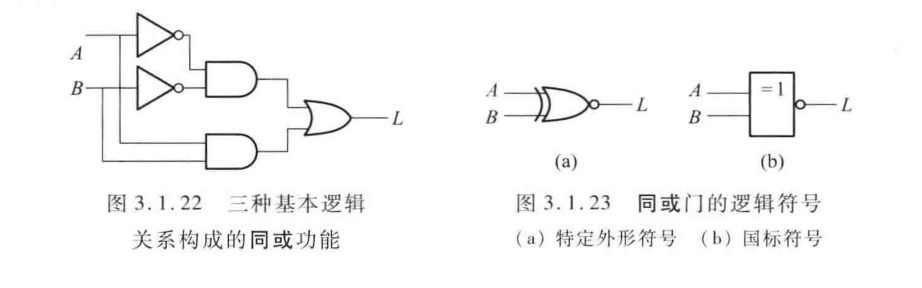

8.同或逻辑关系

3.1.3集成逻辑门电路的结构和特性

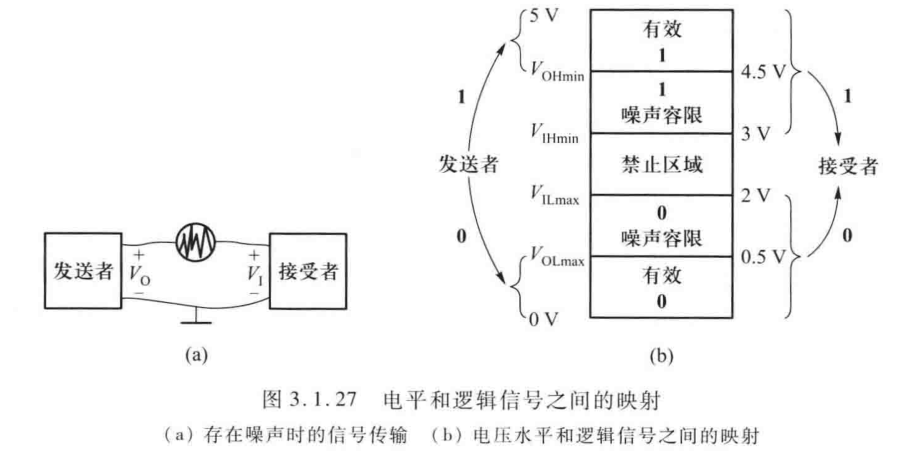

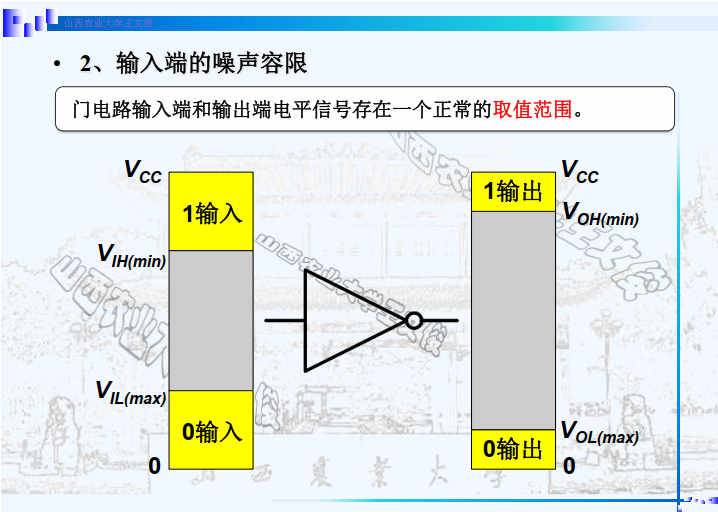

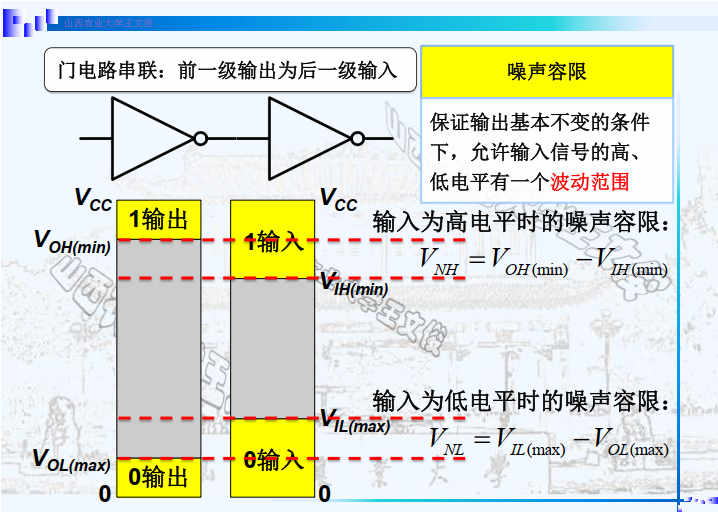

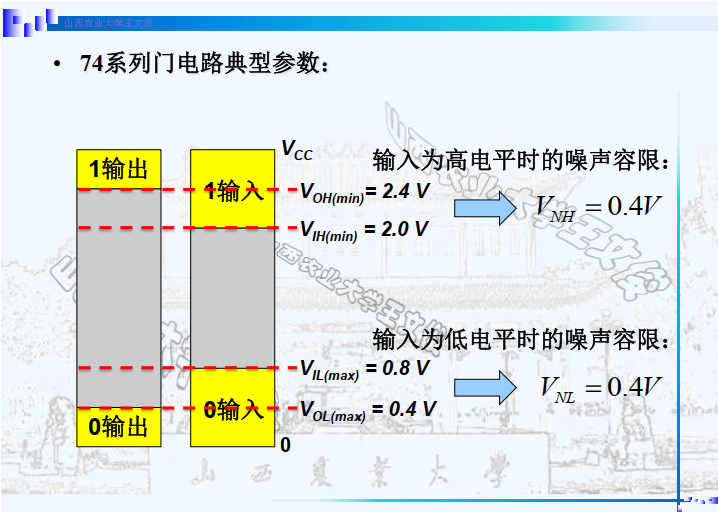

3.3.1 逻辑电平与噪声容限

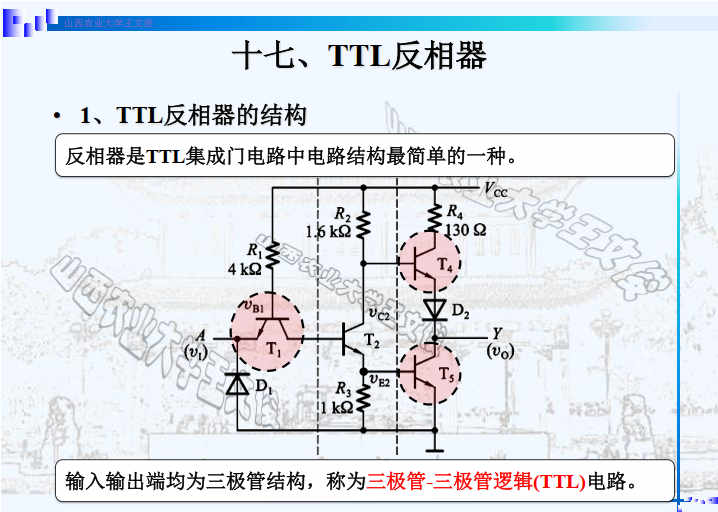

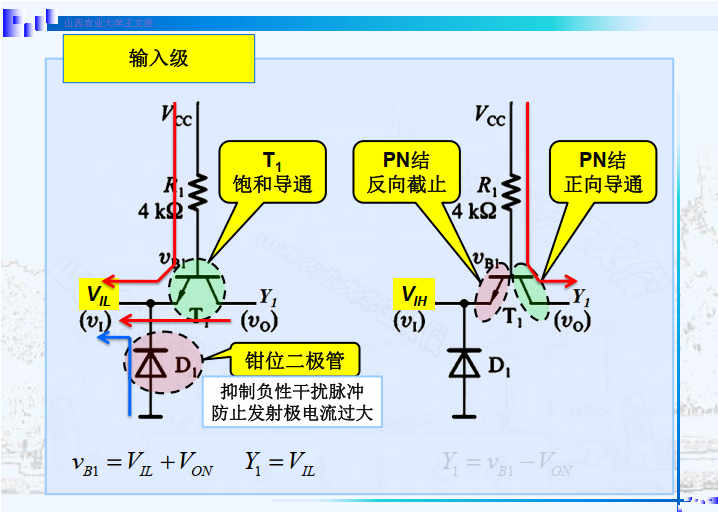

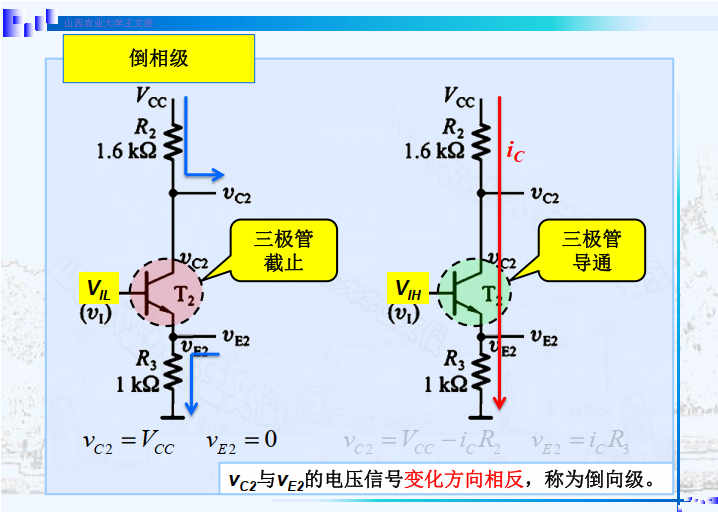

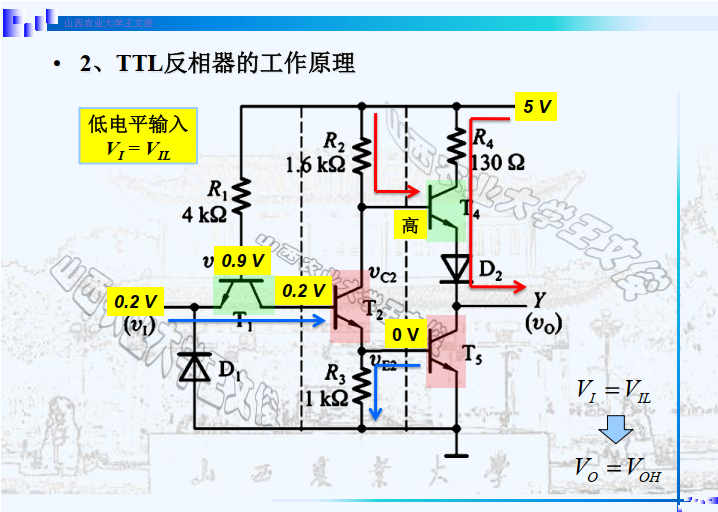

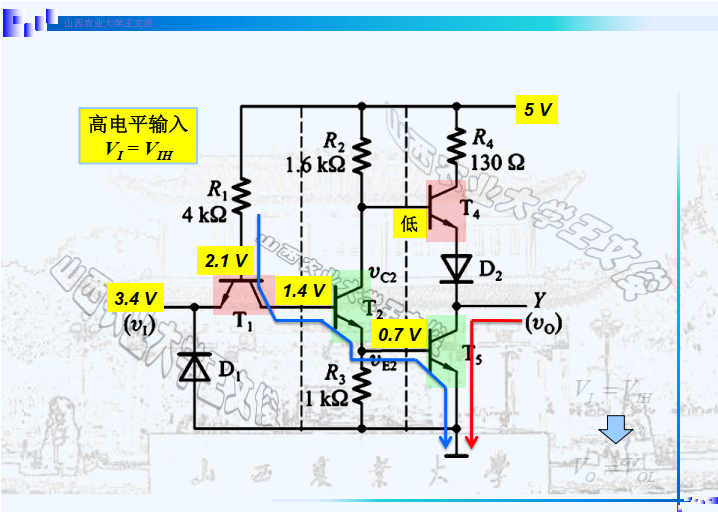

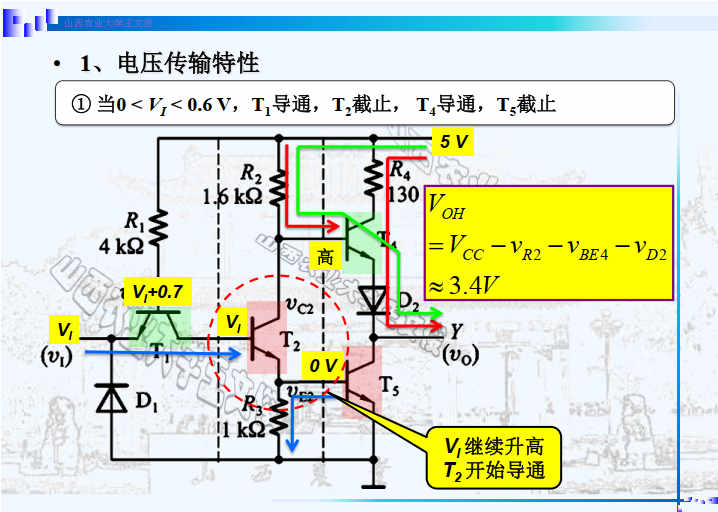

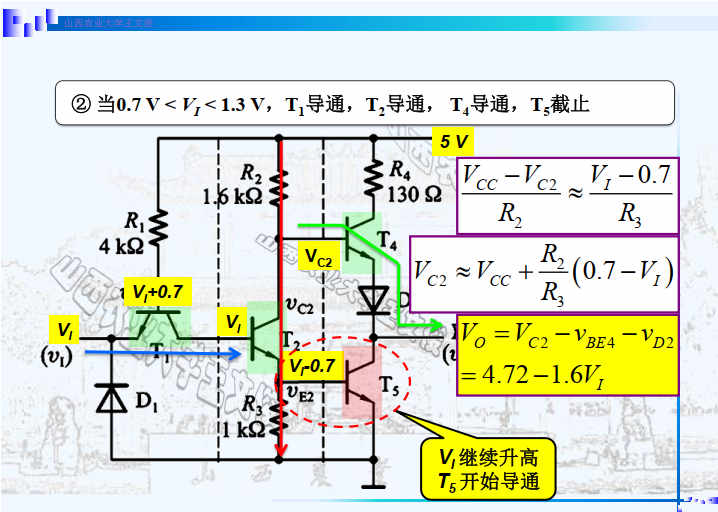

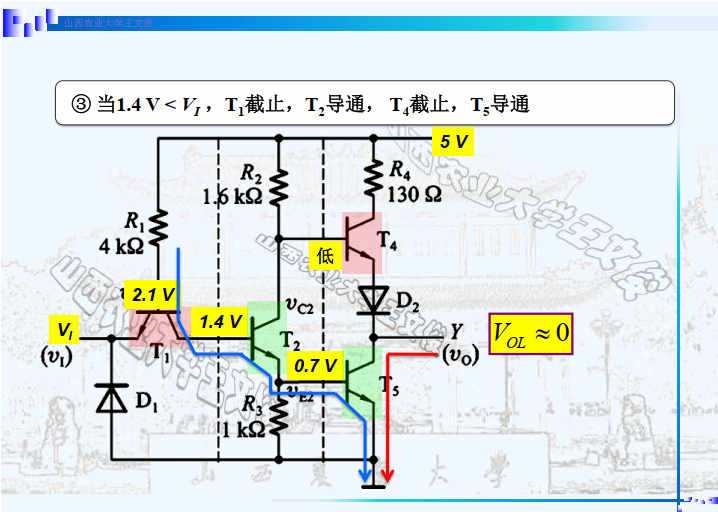

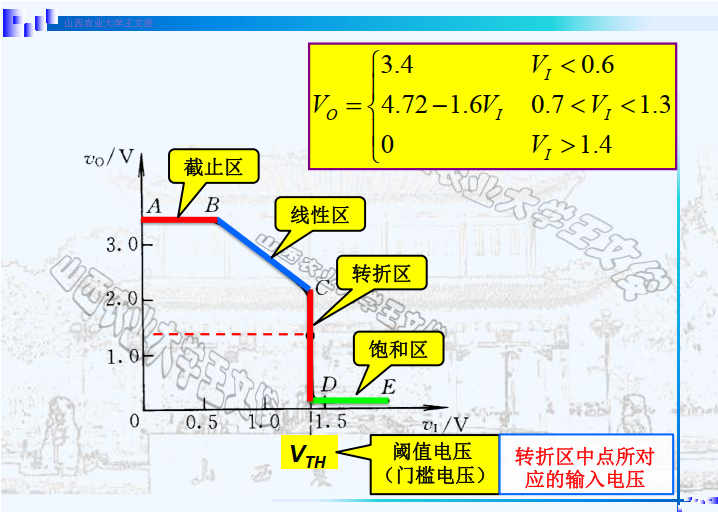

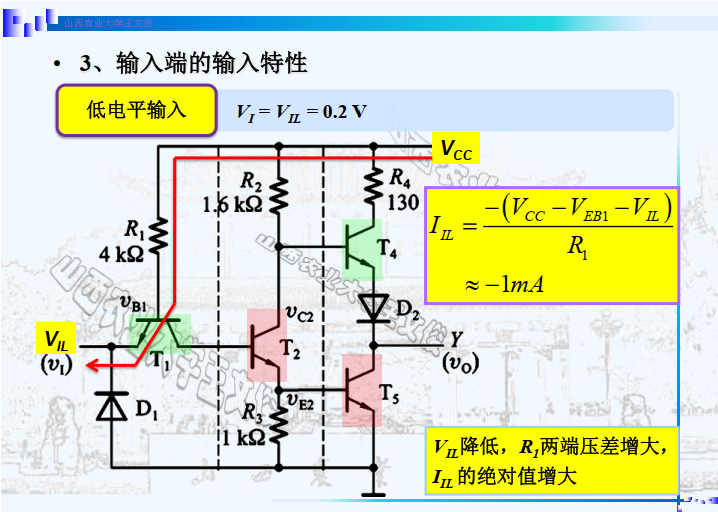

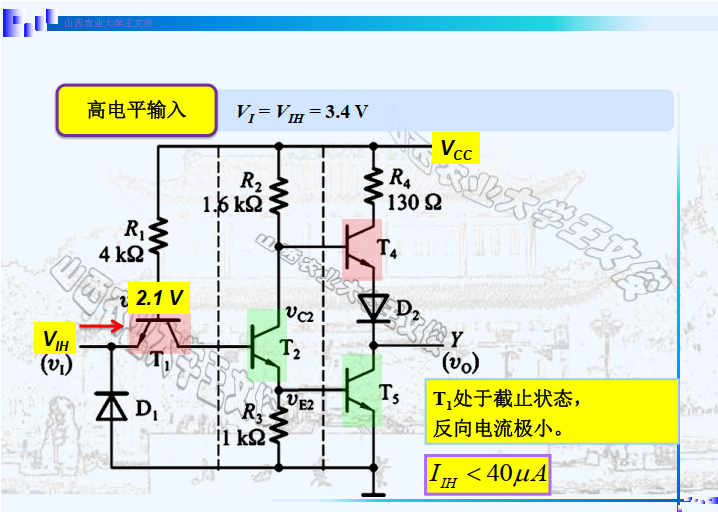

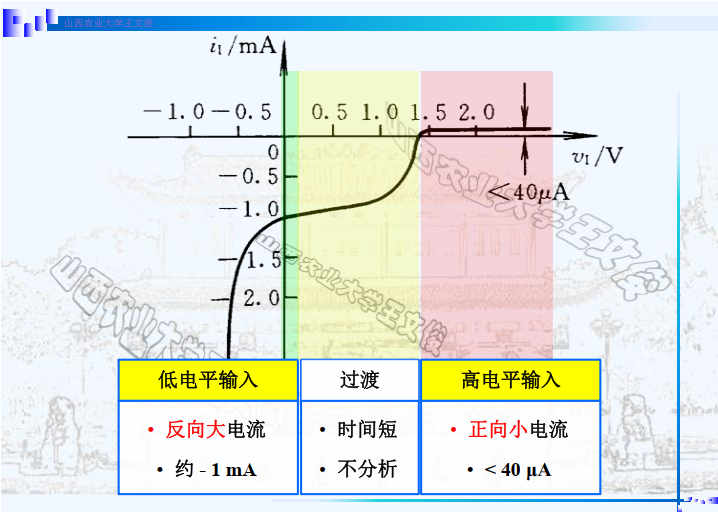

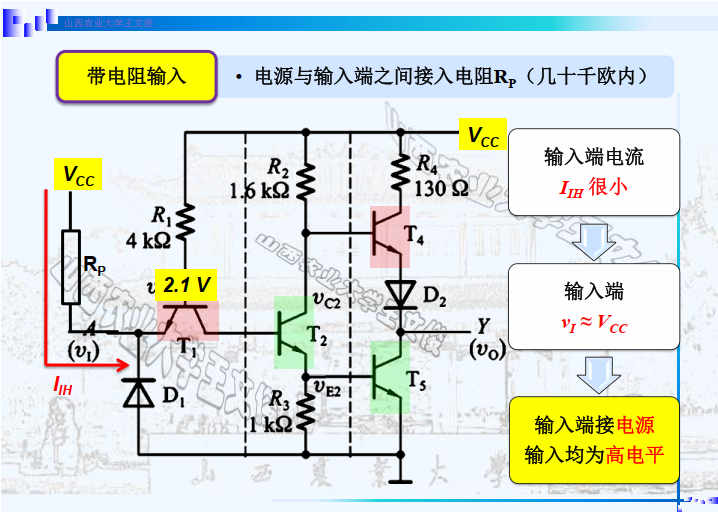

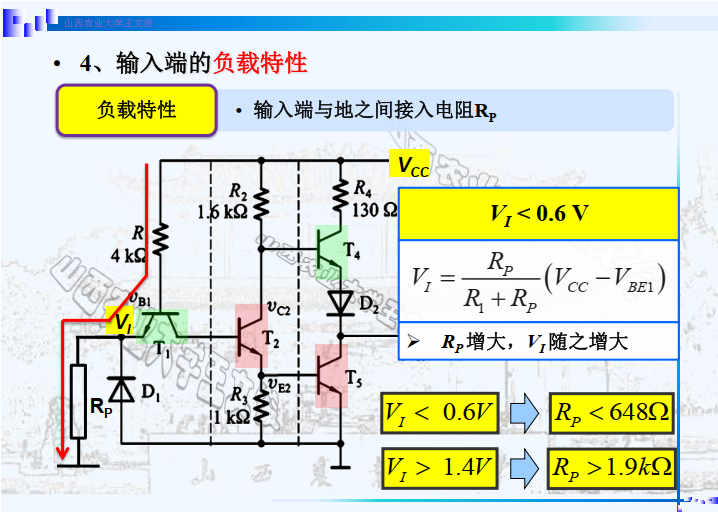

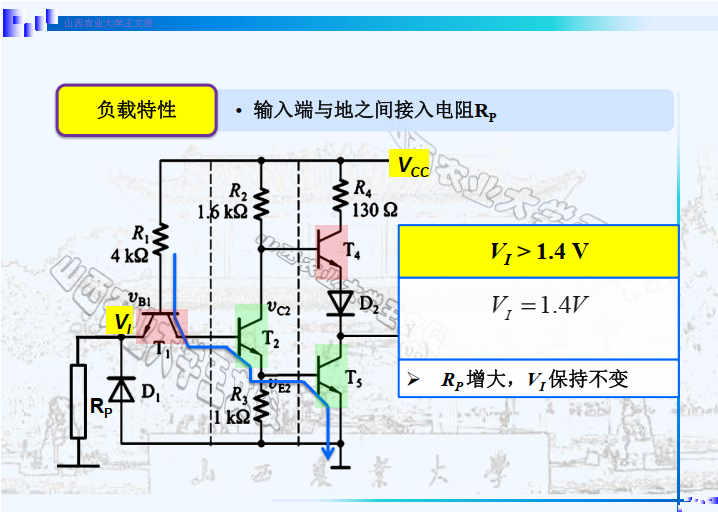

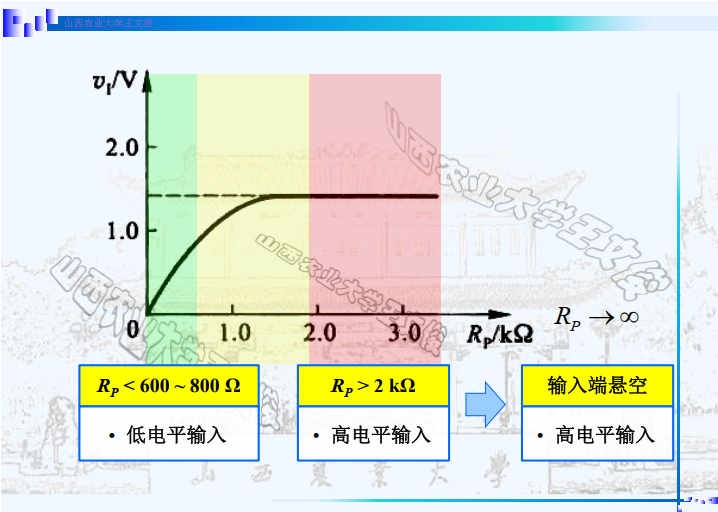

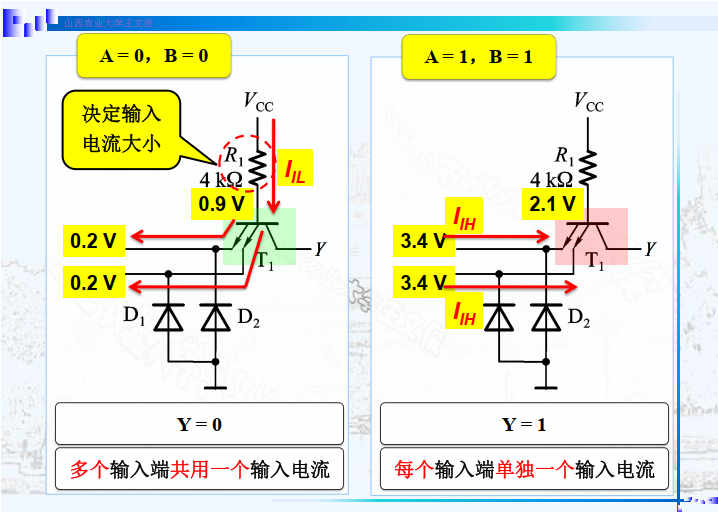

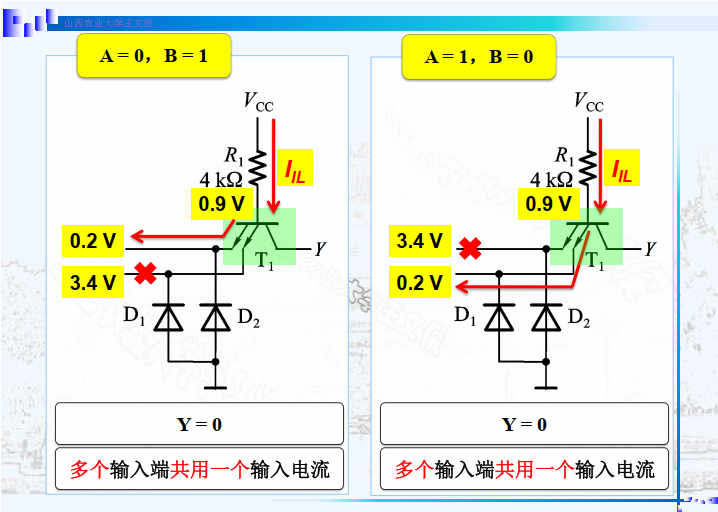

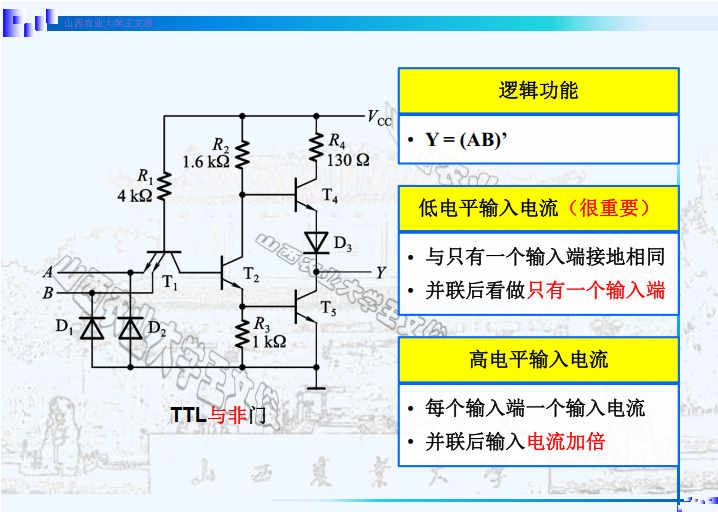

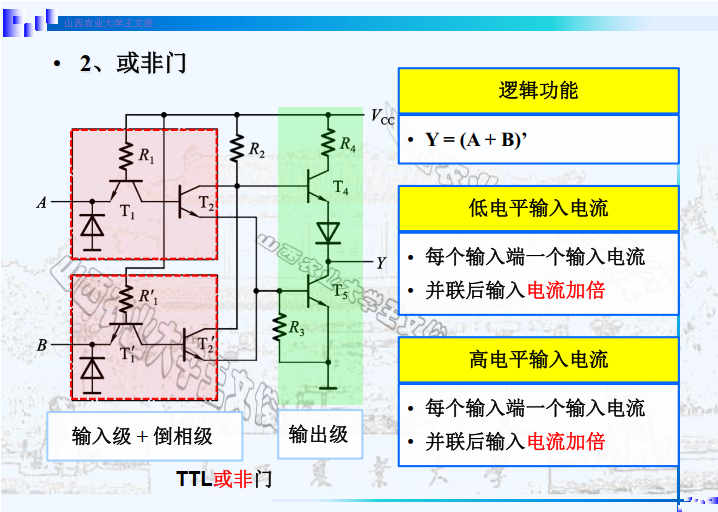

3.3.2 TTL集成逻辑门

TTL集成逻辑门

以下PPT来自: B站王文俊【数字电子技术基础】 https://www.bilibili.com/video/BV18Z4y1Q7iq/

Folding 点击查看更多

<p>TODO 此处未整理完,以后再加</p>

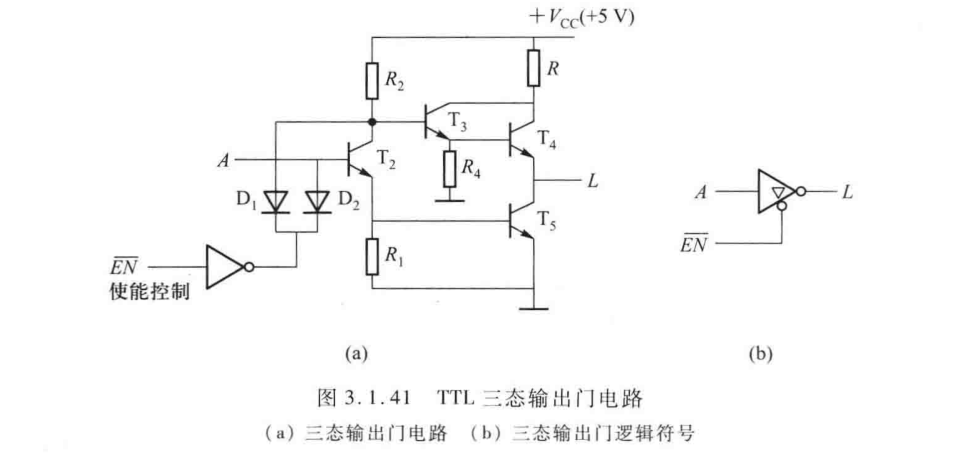

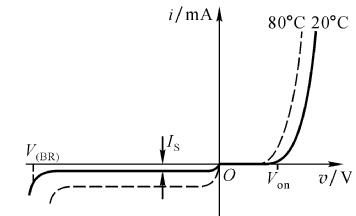

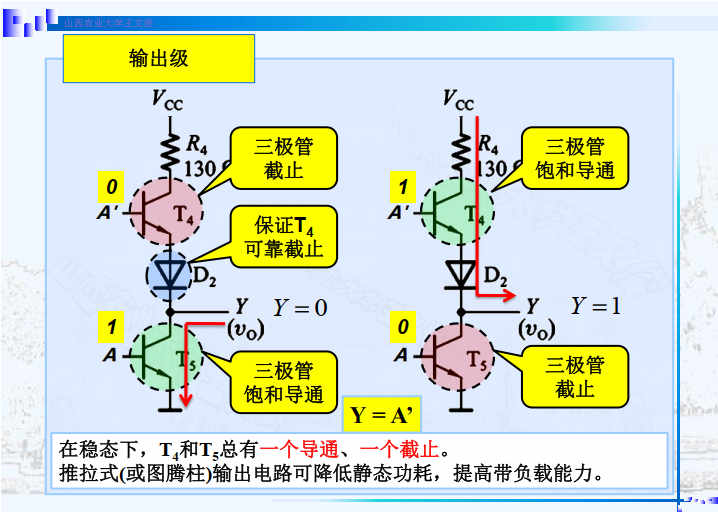

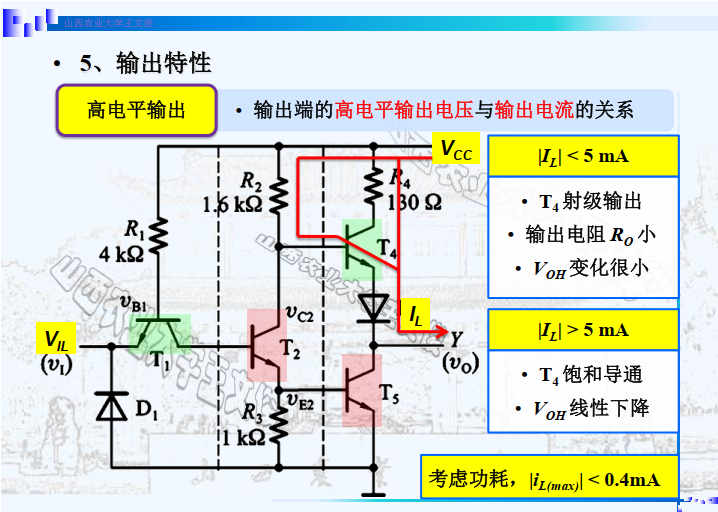

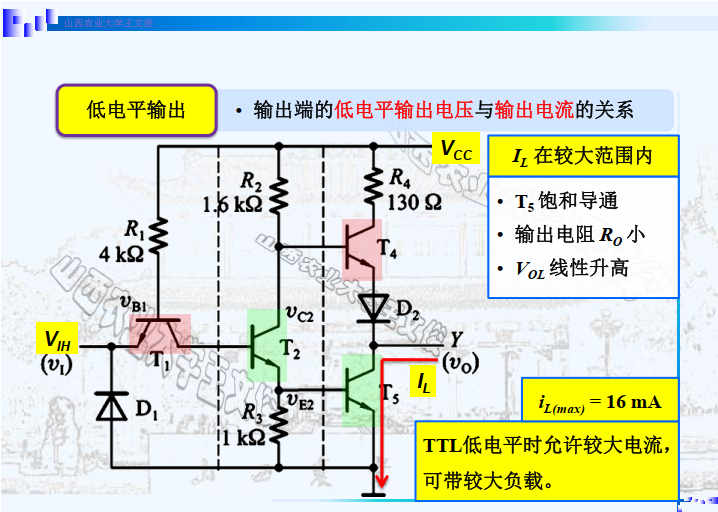

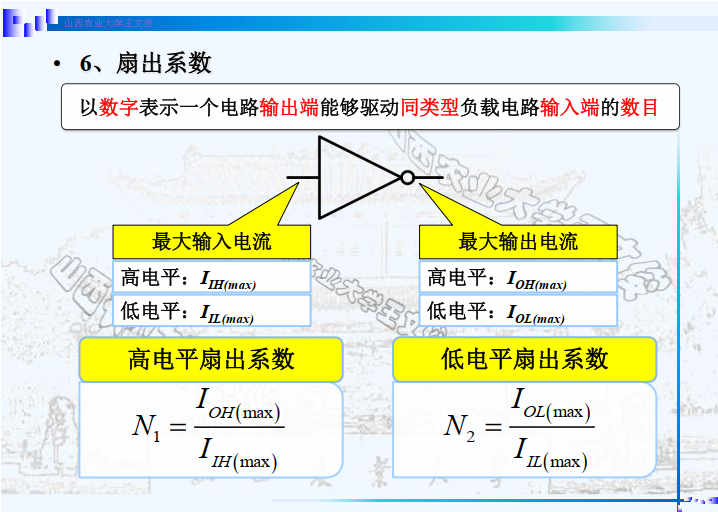

TTL集成门电路的三种输出结构

推拉式结构

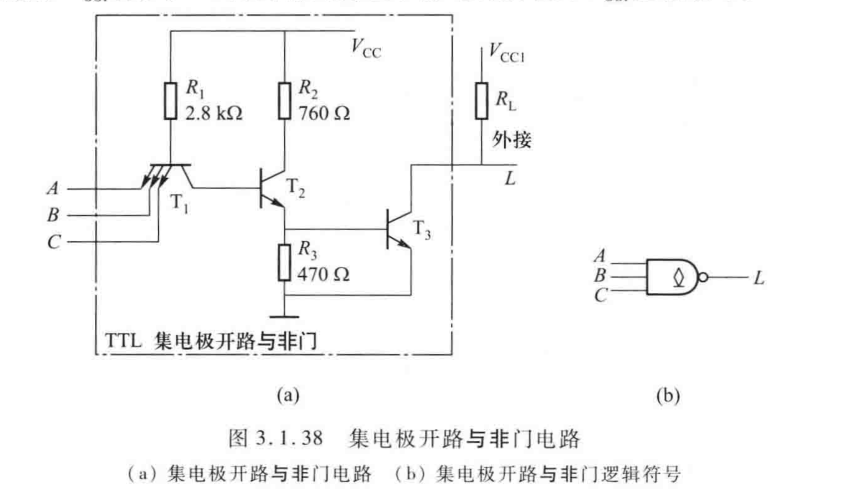

集电极开路结构(OC门) OC门只有输出逻辑0和开路(或悬空,高阻)两种状态。为了防止0C门输出逻辑状态不确定,使用时0C门输出必须外接上拉电阻

OC门的典型应用如下:

OC门的典型应用如下:(1)实现线与的逻辑功能。0C门的输出端可以直接连在一起,共用上拉电阻和电源,实现线与逻辑功能。线与连接的OC门实现了与或非的逻辑功能。如图3.1.39。逻辑表达式为:

(2)实现两种逻辑电平转换。0C门外接负载所用的电源可以和门电路的电源Vcc一致,也可采用不同于Vc的另一组电源如图3.1.38(a)中的Vcc,以改变或提高输出高电平值,实现逻辑电平的转换。

(3)实现电平指示。 如图3.1.40,0C门外接的上拉电阻

三态输出结构 除了输出高电平1和低电平0以外,还有高阻态输出。

3.3.3 CMOS集成逻辑门

TODO 此处未整理完

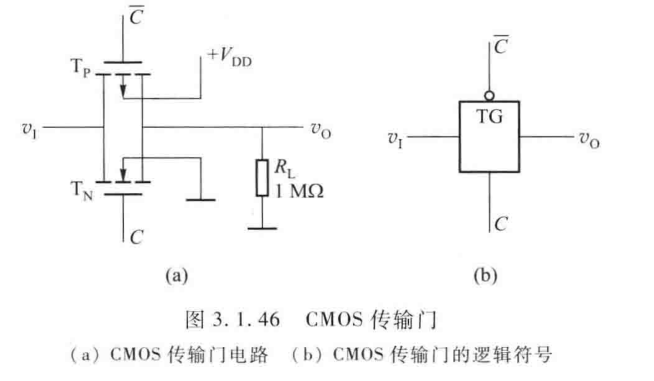

CMOS传输门(TG门(Transmission Gate))

不但能传输逻辑电平,还能够传输模拟电压,常用于构成多路模拟开关。TG门的内部电路和逻辑符号如图3.1.46所示。

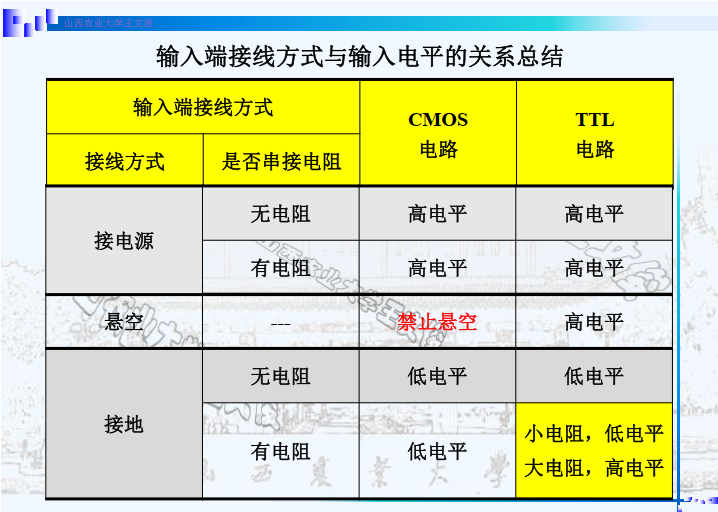

3.3.4门电路使用注意事项

- 多余输出端的处理

- 与和与非功能,多余输入端接正电源(逻辑1),或与使用端并联

- 或和或非功能,多余输入端接地(逻辑0),或者和使用端并联

-

TODO 此处未整理完,以后再加

3.1.4逻辑代数

#### 常用公式:

#### 运算规则:

代入规则 e.g.

对偶规则 若将

反演规则 若将

#### 卡诺图:

- 5变量卡诺图:以中心轴对称的小方格代表最小项相邻。

易错点

- 6->5->4->3->2->1->0->6 7进制减法计数器

- 采用奇校验方式传输11010010时 时 ,需增加的校验位为:1 。

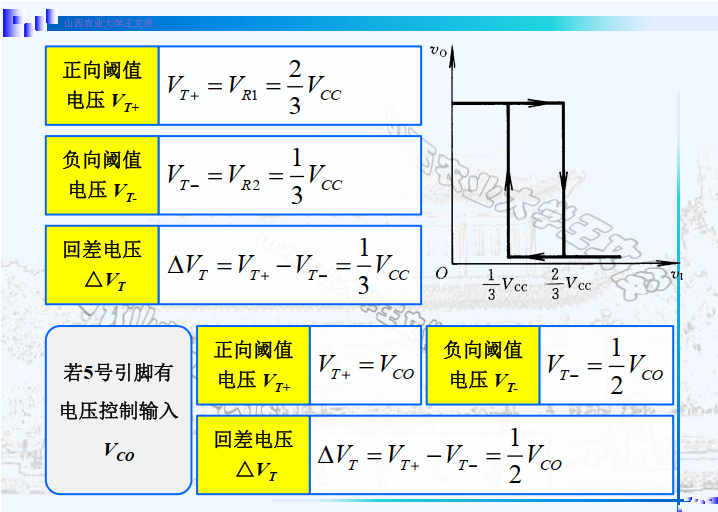

555定时器

1、接成施密特触发器

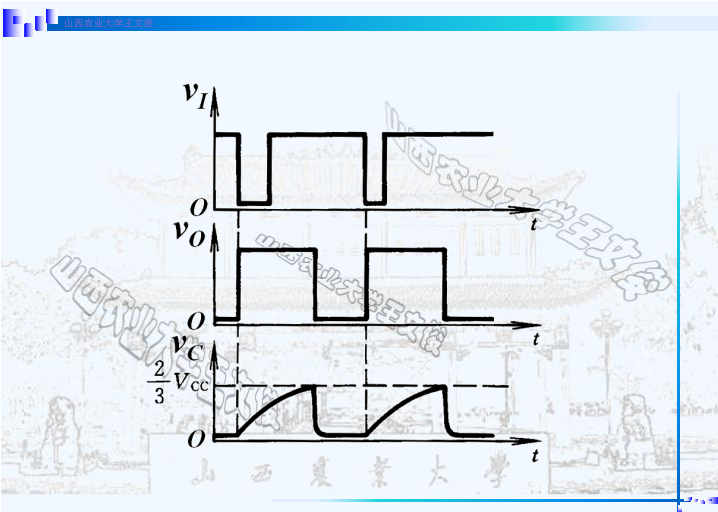

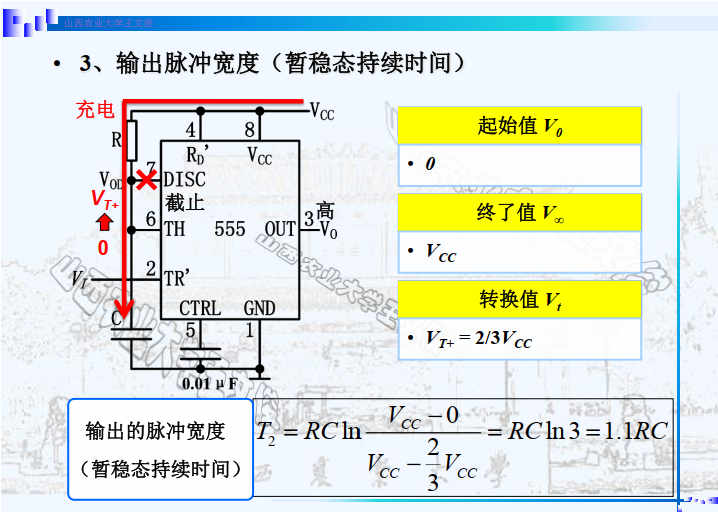

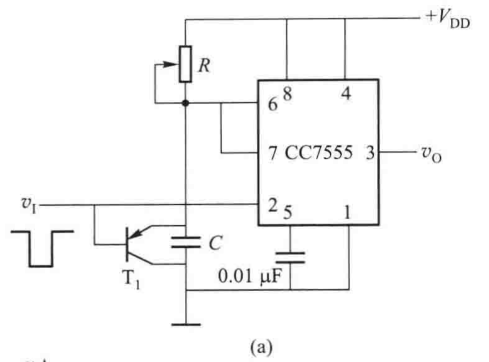

2、单稳态触发器

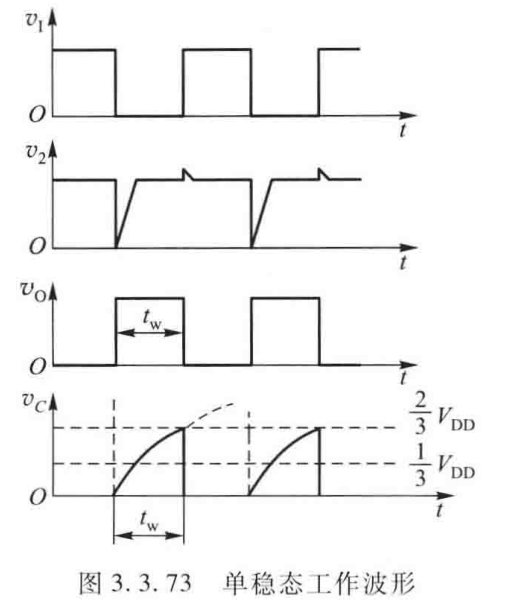

不可重复触发:

不可重复触发:

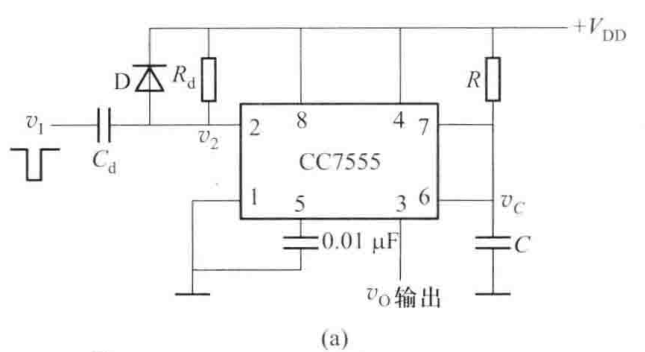

可重复触发:

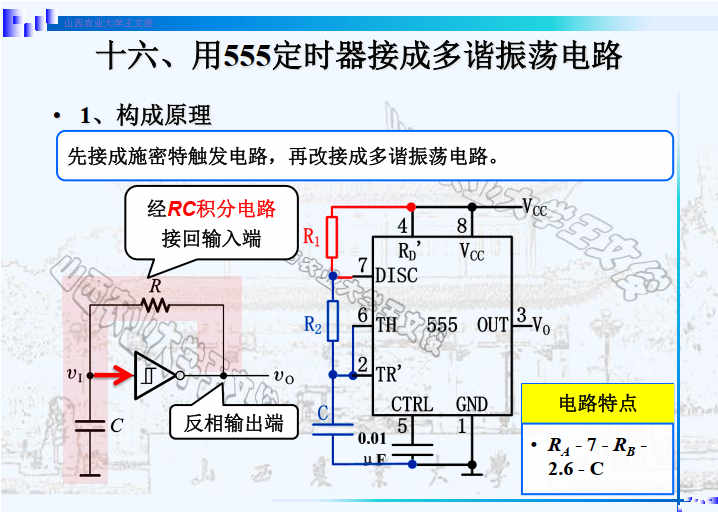

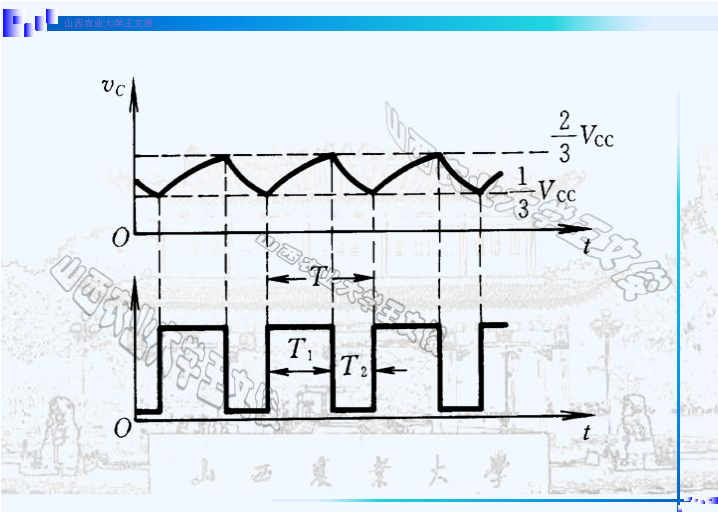

3、多谐震荡电路

3.2基本逻辑电路的分析与设计

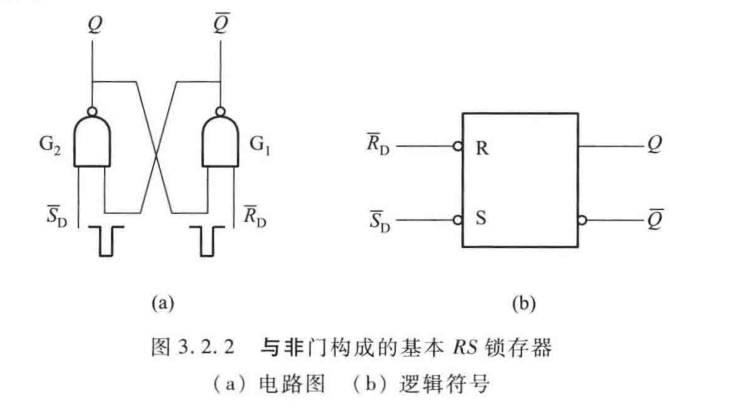

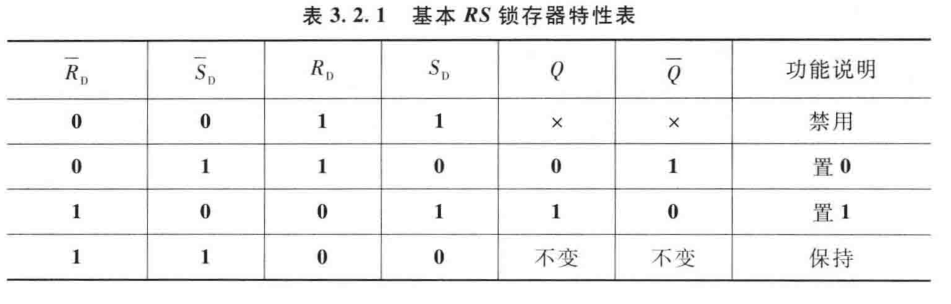

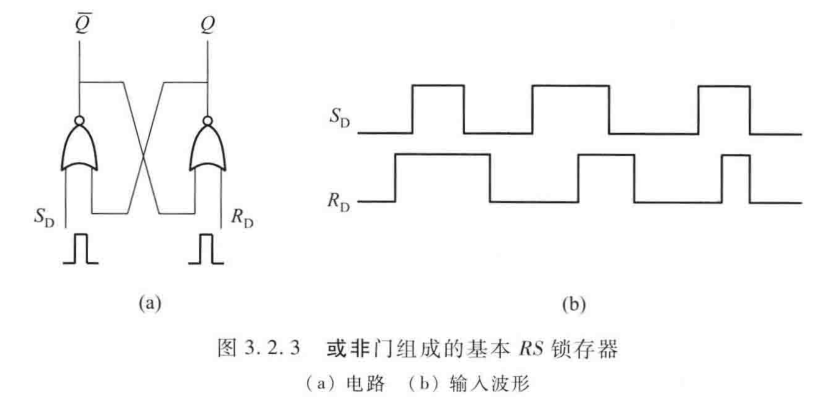

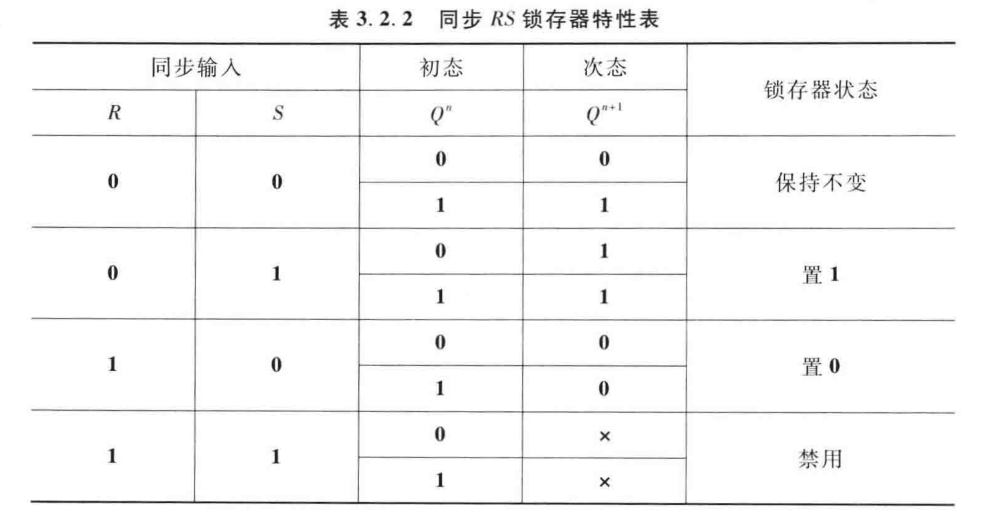

3.2.1锁存器、触发器与定时器

基本RS锁存器

同步RS锁存器(门控RS锁存器)

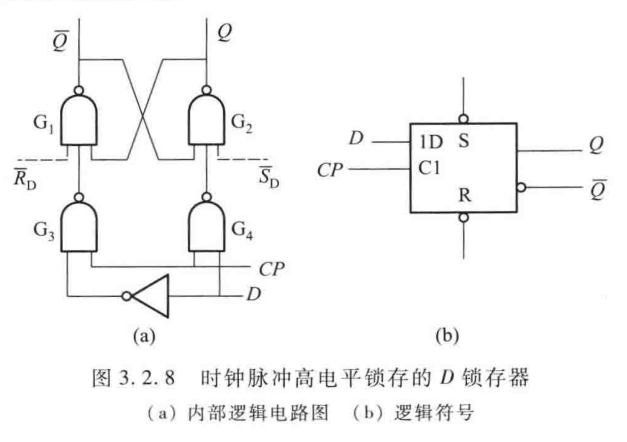

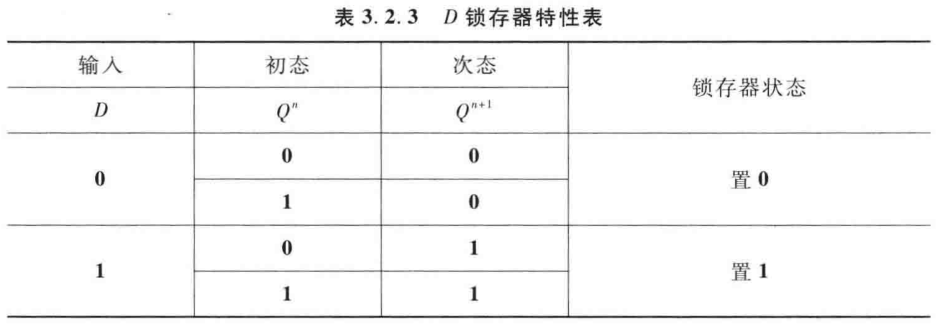

同步D锁存器

边沿触发的 RS触发器

TODO 此处未整理完,以后再加

OC门的典型应用如下:

OC门的典型应用如下: